#### DISSERTATION

# RAPID EARLY DESIGN SPACE EXPLORATION USING LEGACY DESIGN DATA, TECHNOLOGY SCALING TREND AND IN-SITU MACRO MODELS

Submitted by

Charles V.K. Thangaraj

Department of Electrical and Computer Engineering

In partial fulfillment of the requirements for the Degree of Doctor of Philosophy Colorado State University Fort Collins, Colorado Fall, 2009 UMI Number: 3401003

All rights reserved

INFORMATION TO ALL USERS The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

UMI 3401003 Copyright 2010 by ProQuest LLC. All rights reserved. This edition of the work is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

#### COLORADO STATE UNIVERSITY

Nov 9, 2009

WE HEREBY RECOMMEND THAT THE DISSERTATION PREPARED UNDER OUR SUPERVISION BY CHARLES V.K. THANGARAJ ENTITLED RAPID EARLY DESIGN SPACE EXPLORATION USING LEGACY DESIGN DATA, TECHNOL-OGY SCALING TREND AND IN-SITU MACRO MODELS BE ACCEPTED AS FULFILLING IN PART REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY.

Committee on Graduate\_Work

George Søllins

Anthony Maciejewski Phillip Chapman

Advisor: Tom Chen

AAnna Department Head: Anthony Maciejewski

### ABSTRACT OF DISSERTATION

# RAPID EARLY DESIGN SPACE EXPLORATION USING LEGACY DESIGN DATA, TECHNOLOGY SCALING TREND AND IN-SITU MACRO MODELS

CMOS technology scaling trend, i.e. the doubling of the operating frequency and the doubling of the number of transistors on a die every eighteen months, also know as Moore's Law has been a fundamental driver for the semiconductor industry for well over three decades. Scaling CMOS technologies into deep sub micron especially into sub 100 nm dimensions have caused a significant shift in business and design philosophy, and methodology. In addition to the semiconductor industry maturation there are seven key disruptive trends impacting the semiconductor industry. They are competitive landscape changes, technology convergence, greater global connectedness, increased design complexity, commoditization, consumerization, and the soaring research, development and engineering costs. These disruptions have made traditional business models increasingly ineffective and the benefits of Moore's Law insufficient for sustained competitiveness [1]. 'More-than-Moore' approach to heterogeneous system integration and holistic system optimization strategies in addition to the benefits of technology scaling are necessary for future success [2] [3].

Embedded computation systems and microprocessor designs have significantly benefitted from "cramming" more transistor on a single die. When memory is included on die (with large amounts of cache on die) the latency incurred in moving data and instructions to the computation units reduces sharply, increasing the overall instruction execution rate and ultimately increasing performance. Increase in operating frequency being another aspect of technology scaling, improves the number of instruction executed per unit time. In a superscalar execution pipeline, increasing operating frequency increases overall instruction execution rate and throughput. The conventional design flow for computation engines (embedded computation systems and microprocessors) starts with architectural design followed by physical design. In nanometer CMOS technologies, successful physical implementation of a highly optimized architectural design is not guaranteed due to power consumption variations, signal integrity and processing challenges.

Consequently, design convergence in both power and performance have become increasing difficult with increasing levels of system integration, design complexity and technology scaling related uncertainties. As a result, traditional compartmentalized design methodologies are no longer sufficient as they lead to designs that are pessimistic, slow and/or power hungry. A holistic and systematic understanding of the various design tradeoffs and exploring the design solution space extensively early in the design phase improves design convergence. Some design challenges can be best addressed at the circuit level, others are most effectively addressed at the architecture or system level. With increasingly competitive business conditions dictating design cycle times and time-to-market window, a thorough design space exploration at an early stage of a design can put the design in an optimal subspace for better convergence and for avoiding costly redesigns later on in the design cycle. Rapid and effective design space exploration at all stages of a design process enables faster design convergence and meeting time-to-market stipulation. Design space exploration is important and particularly effective during the early stage of a design where design decisions can have a significant impact on design convergence. A holistic approach to system design is possible only when design tools and aids that incorporate high

level system models are easily available to perform tradeoff analysis and design space exploration.

This work proposes a system level design framework for early design space exploration with a focus on power and performance tradeoffs using analytical power and performance prediction models. The analytical prediction models are driven by legacy design data, technology scaling trend, low level physical design parameters and in-situ simulations. Experiments on ISCAS benchmark circuits validate the feasibility of the proposed approach and yielded power centric designs that improved power by 7% - 32% for a corresponding 0% - 9% performance impact; or performance centric designs with improved performance of 11.25% - 17% for a corresponding 2% - 3.85% power penalty. Evolutionary algorithm based Pareto analysis on an industrial 65 nm design uncovered design tradeoffs which are not obvious to designers and optimize both power and performance. The high performance by 29% with a 2.5% power penalty, whereas the low power design option reduced the straight-ported design's power consumption by 40% for a 9% performance penalty.

The design framework and methodology developed and demonstrated in this work form the foundational steps for early design space exploration utilizing technology scaling trends, process dependent parameters and in-situ simulations. Analytical prediction models are currently limited only to predicting power and performance. Prediction models for yield, chip area and system reliability are seen as valuable future additions to EIDAs capability. Modeling the impact of process variation and the ability to incorporate statistical inputs and outputs are seen as an another incremental improvement to EIDAs value as a design tool. In addition to the above improvements, a macromodel based critical path delay calculation technique including clock and signal uncertainties, incorporating special libraries, RF and analog modules in the system model and, improving the evolutionary algorithm used for design space exploration are salient direction for future research.

> Charles V.K. Thangaraj Department of Electrical and Computer Engineering Colorado State University Fort Collins, Colorado 80523 Fall, 2009

#### ACKNOWLEDGEMENTS

"If I have seen further than others, it is by standing upon the shoulders of giants." - Sir Isaac Newton

"The horse is made ready for the day of battle, but victory rests with the LORD." - Proverbs 21:31

I am forever grateful to my graduate advisor, Dr. Tom Chen, for his constant support and guidance in the pursuit of my academic goals.

I thank Dr. George Collins, Dr. Anura Jayasumana, Dr. Anthony Maciejewski and Dr. Philip Chapman, members of my graduate committee, for their support throughout the program. I would also like to specifically thank all members of the VLSI System Architecture Lab, Colorado State University, for their invaluable help and support.

Special thanks to Bea & Carl Mohr and the Mohr family, Lynn & Jeffrey Smith, for their well wishes and many friends who where with me through thick and thin. I would also like to thank all my teachers from Stanes High School, Kumaraguru College of Technology and Colorado State University on who's shoulders I stand. Last but not the least, I thank my lovely parents and brother, for being my constant source of inspiration and for having faith in me.

Above all, I humbly give all glory to my Lord Almighty for His grace and blessings to undertake this arduous journey, without whom nothing is possible !

# CONTENTS

. . . . .

| 1 Introduction                                               |                                       | 1  |

|--------------------------------------------------------------|---------------------------------------|----|

| 1.1 CMOS Technology Scaling                                  |                                       | 1  |

| 1.1.1 Technology Scaling and System Level Design             |                                       | 4  |

| 1.2 Semiconductor Industry Trends and Challenges             |                                       | 6  |

| 1.2.1 Business Trends                                        |                                       | 6  |

| 1.2.2 Manufacturing Technology Cost Challenges               |                                       | 7  |

| 1.2.3 Design and EDA Tool Challenges                         |                                       | 9  |

| 1.3 Motivation and Objective                                 |                                       | 11 |

| 2 Background Information, Existing Methodologies             | and Approaches 1                      | 3  |

| 2.1 Overview                                                 | 1                                     | 13 |

| 2.2 System Level Power Performance Optimization              | 1                                     | 14 |

| 2.2.1 SimpleScalar Toolset                                   | 1                                     | 16 |

| 2.2.2 SimplePower Toolset                                    |                                       | 19 |

| 2.2.3 Wattch Toolset                                         |                                       | 22 |

| 2.2.4 AccuPower Toolset                                      | · · · · · · · · · · · · · · · · · · · | 25 |

| 2.2.5 PowerTimer Toolset                                     | · · · · · · · · · · · · · · · · · · · | 27 |

| 2.3 RT-Level Power Performance Optimization                  |                                       | 31 |

| 2.4 Physical Level Power Performance Optimization            | · · · · · · · · · · · · · · · · · · · | 35 |

| 2.4.1 BACPAC Toolset                                         | · · · · · · · · · · · · · · · 3       | 38 |

| 2.5 Shortcomings of Existing Tools and Methodologies $\dots$ | 4                                     | 11 |

| 3 The Proposed Approach                                      | 4                                     | 15 |

| 3.1 Overview                                                 | 4                                     | 45 |

| 3.2 Proposed High Level Modeling Methodology                 | 4                                     | 15 |

| 3.3 Module Descriptor Vector Elements                        | 4                                     | 19 |

| 3.3.1 Legacy Design Descriptors                              |                                       | 50 |

| 3.3.2 Target Process Technology Descriptors                  |                                       | 51 |

| 3.3.3 In-situ Simulations and Descriptors                    | 5                                     | 52 |

| 3.4 Proposed Analytical Power and Performance Modeling       | Methodology5                          | 54 |

| 3.4.1 Dynamic Power                                          | 1                                     | 54 |

| 3.4.2 Leakage Power                                          |                                       | 56 |

| 3.4.3 Operating Frequency                                    |                                       | 58 |

| 3.4.4 Effect of $V_{dd}$ Scaling                             | Ę                                     | 59 |

| 3.4.5 Procedure to Find Coefficients X and Y in Eqn 3.26                     | 61        |

|------------------------------------------------------------------------------|-----------|

| 3.4.6 Procedure to Find ABBC, ABBPC, STC, STPC and DVTC Descriptors          | 62        |

| 3.5 Proposed Methodology for Rapid Early Design Space Exploration            | 66        |

| 3.5.1 Estimating Module Power and Performance                                | 66        |

| 3.5.2 System Design Target Prediction                                        | 67        |

| 3.5.3 Design Space Exploration                                               | 67        |

| 3.5.4 Evolutionary Algorithms for Design Space Exploration                   | 70        |

| 4 Proposed Design Space Exploration Methodology: Experimenta                 | 1         |

| Setup                                                                        | <b>71</b> |

| 4.1 Overview                                                                 | 71        |

| 4.2 Experiments in Technology Node Migration                                 | 72        |

| 4.2.1 Applying Module Granular Circuit Level Design Choice                   | 74        |

| 4.3 Design Target Prediction Accuracy                                        | 75        |

| 4.3.1 Successive Design Porting From 180 nm to 65 nm Technologies            | 76        |

| 4.3.2 Design Space Exploration of the Test Circuit in 32 nm Technology       | 78        |

| 4.4 Evolutionary Algorithm Based Design Space Exploration                    | 79        |

| 4.4.1 Design Migration                                                       | 80        |

| 4.4.2 Pareto-Analysis Using Randomized Design Generation                     | 80        |

| 4.4.3 Pareto-Analysis Using EA Based Design Generation                       | 85        |

| 5 Experimental Results, Discussion of the Results and Future Work            | 89        |

| 5.1 Results of Experiments In Technology Node Migration                      | 89        |

| 5.1.1 Technology Node Migration Experiment Observations                      | 98        |

| 5.2 Results of Design Target Prediction Accuracy                             | 100       |

| 5.2.1 Results of Successive Design Porting From 180 nm to 65 nm Technologies | s100      |

| 5.2.2 Results of Design Space Exploration of the Test Circuit in 32 nm Tech- |           |

| nology                                                                       | 102       |

| 5.3 Results of Evolutionary Algorithm Based Design Space Exploration         | 103       |

| 5.3.1 Results of Pareto-Analysis Using Randomized Design Generation          | 103       |

| 5.3.2 Results of Pareto-Analysis Using EA Based Design Generation            | 109       |

| 5.3.3 Pareto-Front Decrowding Replacement Schemes                            | 110       |

| 5.3.4 Figures of Merit: Stoping Criteria                                     | 112       |

| 5.3.5 Results of Pareto-Analysis Using the IRRR Scheme on ISCAS89 Circuit    | 117       |

| 5.4 Discussion of the Results                                                | 119       |

| 5.4.1 Impact of ABB Design Choice                                            | 119       |

| 5.4.2 Prediction Model Complexity: Impact of Model Parameters                | 121       |

| 5.4.3 Pareto-front Quality: Impact of Evolutionary Algorithm                 | 124       |

| 5.5 Conclusion                                                               | 125       |

| 5.6 Future Work                                                              | 127       |

| 6 Acknowledgement                                                            | 129       |

## $\mathbf{i}\mathbf{x}$

| A Common Design Techniques Incorporated into the EIDA Tool                                              | 130                      |

|---------------------------------------------------------------------------------------------------------|--------------------------|

| B Code for System Design Target Prediction                                                              | 136                      |

| C Code for EA Based Design Space Exploration                                                            | 142                      |

| D GUI Implementation of EIDA         D.1 Screen Captures of the GUI         D.2 TCL/Tk Code for the GUI | <b>148</b><br>148<br>155 |

| Bibliography                                                                                            | 184                      |

# LIST OF FIGURES

| 1.1  | ITRS clock frequency trend up to the year 2020                                            |    |  |

|------|-------------------------------------------------------------------------------------------|----|--|

| 1.2  | Clock rate for high performance microprocessors from Dec '92 to May '02 $$                |    |  |

| 1.3  | Transistor L, $V_{dd}$ and $V_t$ through 2020                                             |    |  |

| 1.4  | ITRS Roadmap for gate and wire delay through process nodes                                | 5  |  |

| 2.1  | Design flexibility, solution time and tool complexity $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 14 |  |

| 2.2  | System level optimization flows                                                           | 15 |  |

| 2.3  | An overview of SimpleScalar toolset                                                       | 17 |  |

| 2.4  | SimpleScalar pipeline model                                                               | 18 |  |

| 2.5  | SimpleScalar internal organization                                                        | 18 |  |

| 2.6  | SimplePower internal organization                                                         | 20 |  |

| 2.7  | SimplePower switching capacitance table for bit-dependent microarchitec-                  |    |  |

|      | tural blocks                                                                              | 22 |  |

| 2.8  | Wattch internal organization                                                              | 23 |  |

| 2.9  | AccuPower internal organization                                                           | 26 |  |

| 2.10 | PowerTimer internal organization                                                          | 27 |  |

| 2.11 | PowerTimer pipeline model                                                                 | 28 |  |

| 2.12 | PowerTimer microarchitectural block power model                                           | 30 |  |

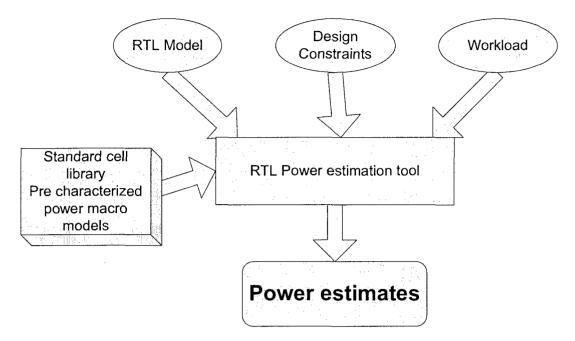

| 2.13 | Typical RTL power estimation flow                                                         | 32 |  |

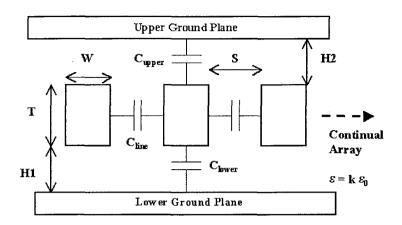

| 2.14 | Interconnect parasitics model                                                             | 39 |  |

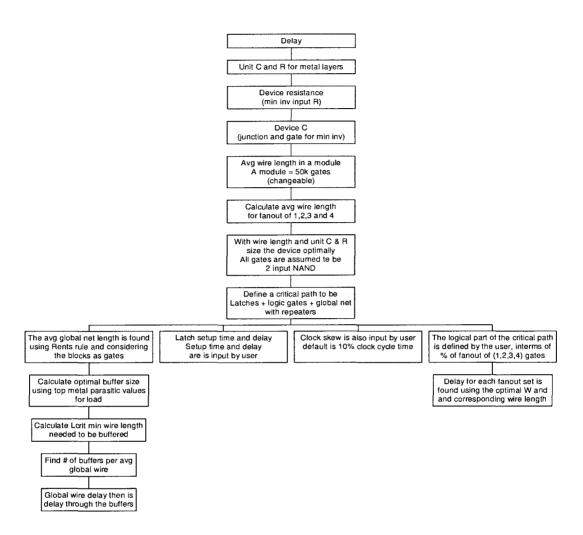

| 2.15 | Steps to estimated delay in BACPAC                                                        | 40 |  |

| 2.16          | Steps to estimated dynamic power in BACPAC                                  | 41 |  |

|---------------|-----------------------------------------------------------------------------|----|--|

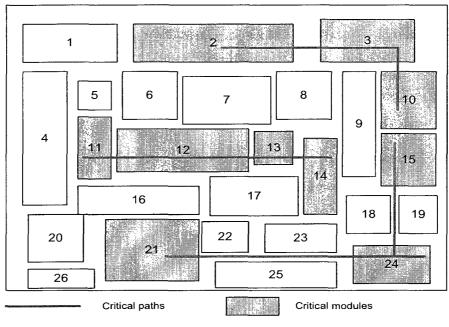

| 3.1           | Critical paths and modules                                                  | 47 |  |

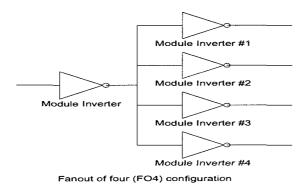

| 3.2           | Fanout of four configuration                                                | 48 |  |

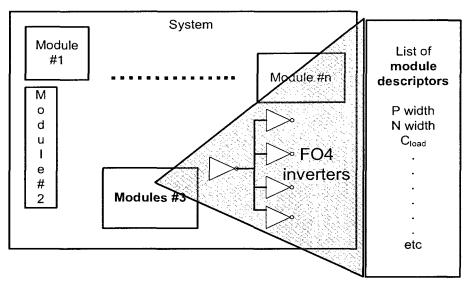

| 3.3           | A partitioned system shown with module $\#3$ abstracted with F04 inverters  |    |  |

|               | and its corresponding descriptor vector                                     | 49 |  |

| $3.4^{\circ}$ | Experiment to obtain STC and STPC factors                                   | 62 |  |

| 3.5           | Experiment to obtain ABBC and ABBPC factors                                 | 64 |  |

| 3.6           | Experiment to obtain DVTC factor                                            | 66 |  |

| 3.7           | Application of a design choice to a module                                  | 67 |  |

| 3.8           | Rapid early design space exploration flow chart                             | 69 |  |

| 4.1           | Benchmark circuit partitioning with critical path shown                     | 73 |  |

| 4.2           | Test system to determine prediction accuracy                                | 76 |  |

| 4.3           | Procedure to compare EIDA and SPICE                                         |    |  |

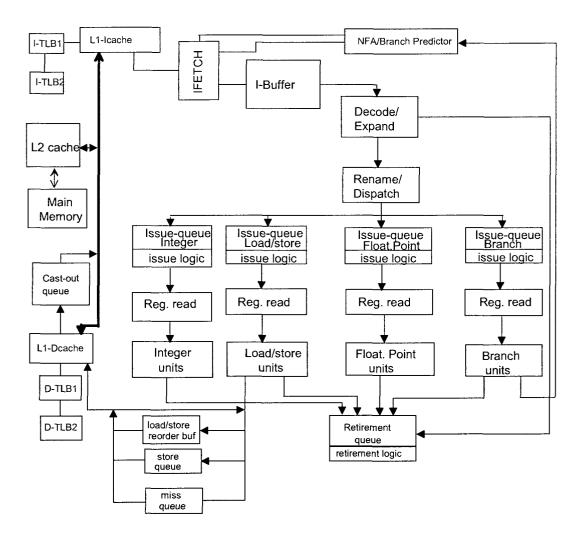

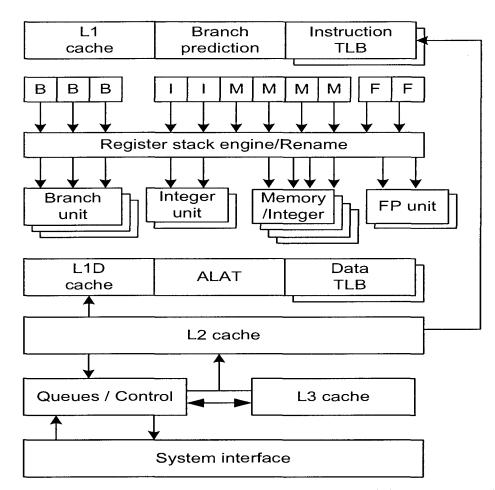

| 4.4           | Block diagram of an modern microprocessor. $B/I/M/FP$ : branch/integer/     |    |  |

|               | memory/ floating point units; ALAT: advanced load address table;            |    |  |

|               | TLB: translation look-aside buffer                                          | 81 |  |

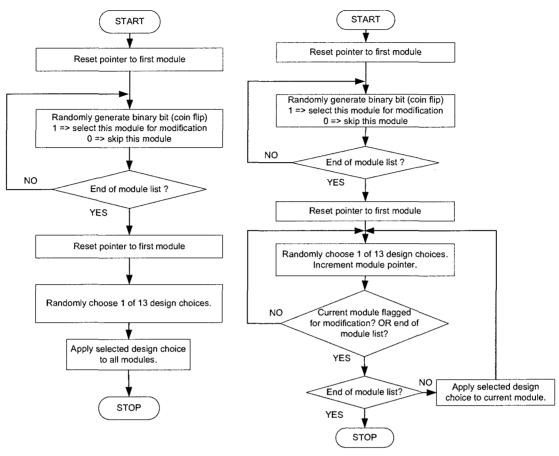

| 4.5           | a) Simple randomizer algorithm b) Complete randomizer algorithm $\ldots$    | 84 |  |

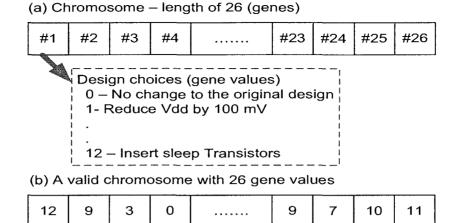

| 4.6           | (a) Chromosome for evolutionary algorithm based pareto analysis. A com-     |    |  |

|               | plete list of all design choices is listed in Table 4.6 (b) A valid chromo- |    |  |

|               | some $(12,9,3,0,\ldots,9,7,10,11)$                                          | 86 |  |

| 5.1           | C5315 design choices                                                        | 91 |  |

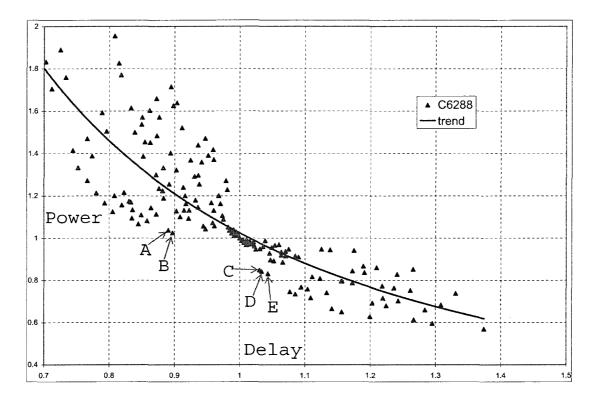

| 5.2           | C6288 design choices                                                        | 92 |  |

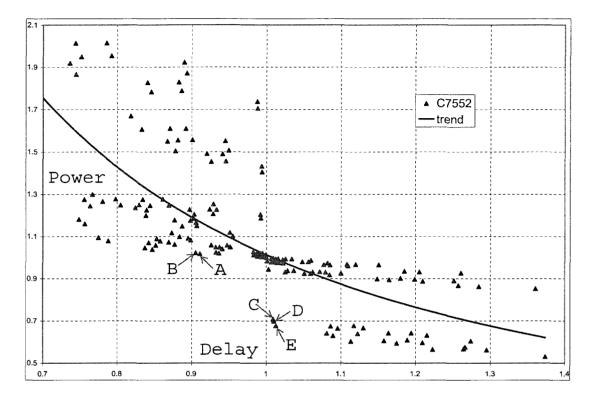

| 5.3           | C7552 design choices                                                        | 93 |  |

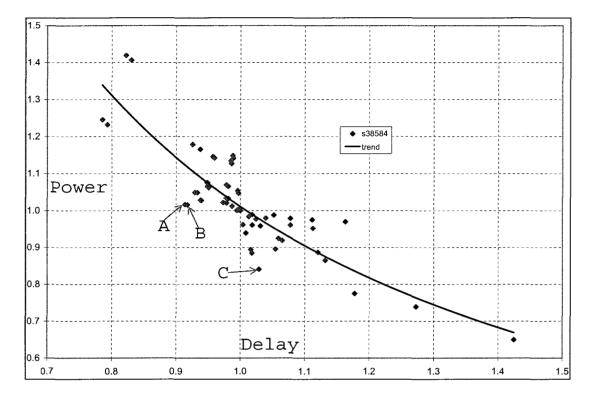

| 5.4           | S38584 design choices                                                       | 94 |  |

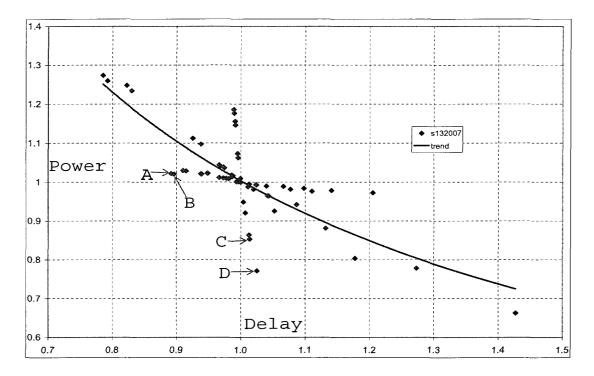

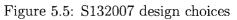

| 5.5           | S132007 design choices                                                      | 95 |  |

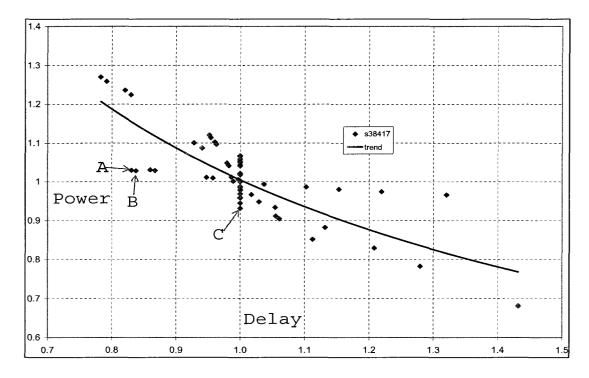

| 5.6  | S38417 design choices                                                                                                              | 95  |  |

|------|------------------------------------------------------------------------------------------------------------------------------------|-----|--|

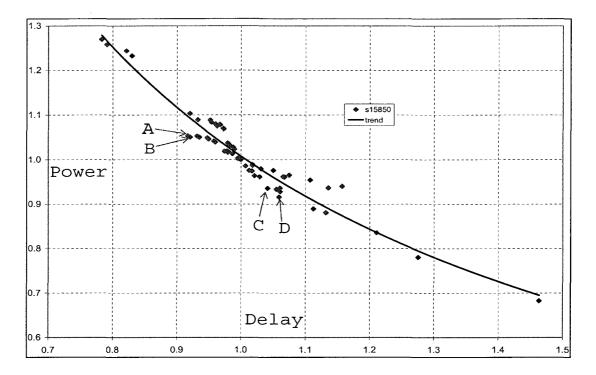

| 5.7  | S15850 design choices                                                                                                              | 97  |  |

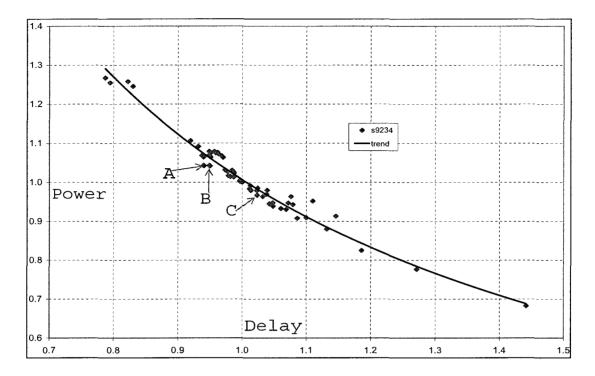

| 5.8  | S9234 design choices                                                                                                               |     |  |

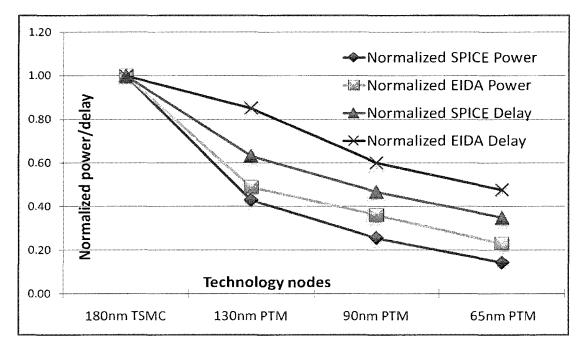

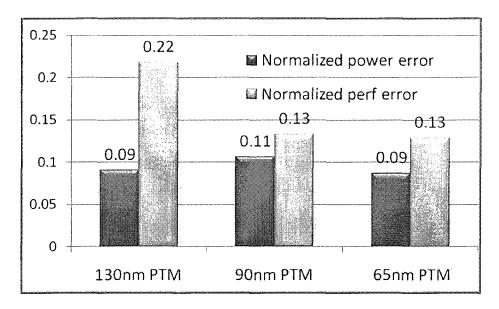

| 5.9  | Observed technology scaling trends for power and performance                                                                       | 100 |  |

| 5.10 | O Observed prediction error with respect to SPICE                                                                                  |     |  |

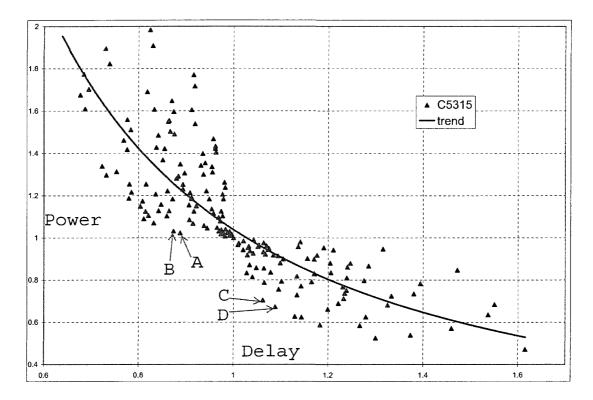

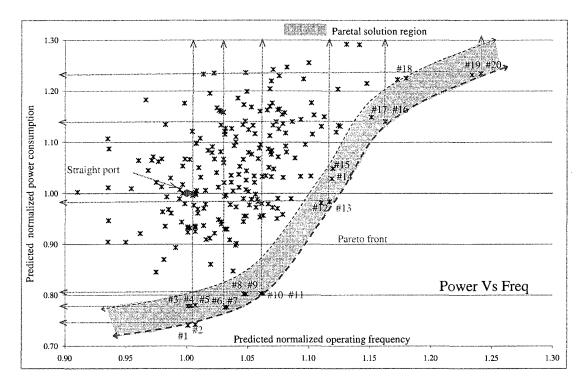

| 5.11 | Pareto-front analysis results                                                                                                      | 104 |  |

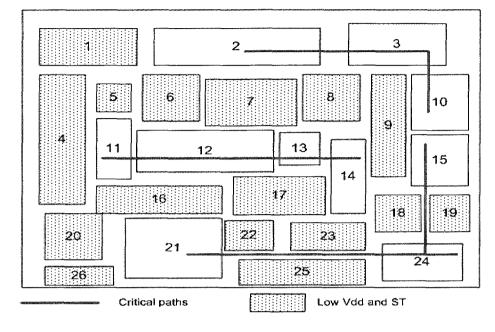

| 5.12 | Design #9 details                                                                                                                  | 106 |  |

| 5.13 | Design #11 details $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                | 106 |  |

| 5.14 | Design 14 details                                                                                                                  | 107 |  |

| 5.15 | Design 13 details                                                                                                                  | 108 |  |

| 5.16 | EA pareto-front progression - baseline with no replacement                                                                         | 109 |  |

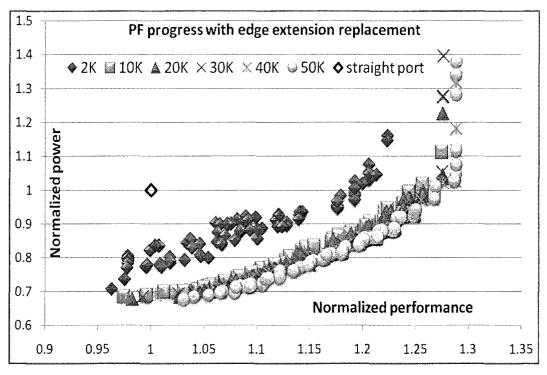

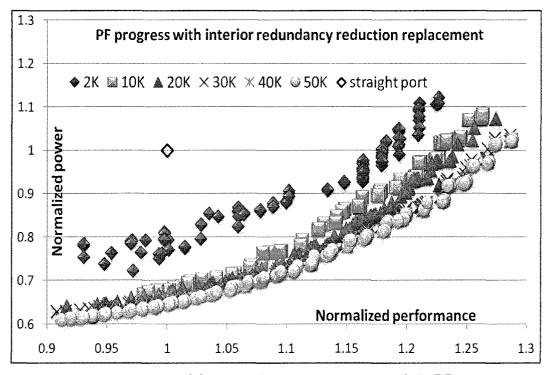

| 5.17 | EA pareto-front progression - with EER                                                                                             | 111 |  |

| 5.18 | EA pareto-front progression - with IRRR                                                                                            | 111 |  |

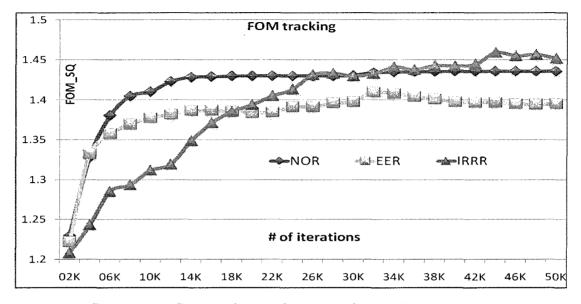

| 5.19 | Figure of merit for pareto-front solution quality                                                                                  | 113 |  |

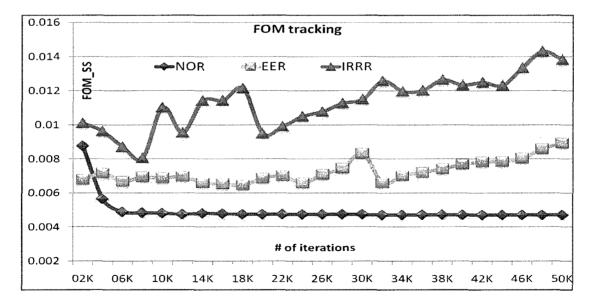

| 5.20 | Figure of Merit for pareto-front solution spread                                                                                   | 113 |  |

| 5.21 | Pareto-front analysis results                                                                                                      | 115 |  |

| 5.22 | Details of system design A from Fig 5.21                                                                                           | 116 |  |

| 5.23 | Details of system design B from Fig 5.21                                                                                           | 117 |  |

| 5.24 | Pareto-front with IRRR at 50K iteration for ISCAS89 s38584 and s38417 $$                                                           |     |  |

|      | circuits                                                                                                                           | 118 |  |

| 5.25 | Figure of merit for ISCAS89 s38584 and s38417 circuits Pareto-front with $% \mathcal{A} = \mathcal{A} = \mathcal{A} + \mathcal{A}$ |     |  |

|      | IRRR solution quality                                                                                                              | 118 |  |

| 5.26 | Figure of Merit for ISCAS89 s38584 and s38417 circuits Pareto-front with                                                           |     |  |

|      | IRRR solution spread                                                                                                               | 119 |  |

| 5.27 | Impact of ABB design choice                                                                                                        | 120 |  |

| A.1  | An illustration for using sleep transistors for power gating                                                                       | 131 |  |

| A.2                                                                       | An illustration for multiple $V_{dd}$ zones in a design                       |       |  |

|---------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------|--|

| A.3                                                                       | An illustration for clock gating technique.                                   |       |  |

| A.4                                                                       | Decoupling capacitance allocation in a standard cell design                   |       |  |

| D 1                                                                       |                                                                               | 1 4 0 |  |

| D.1                                                                       | Invoking the EIDA tool's GUI from the command prompt                          | 148   |  |

| D.2                                                                       | 2 Entering the number of modules in the design                                |       |  |

| D.3                                                                       | 3 Confirming the number of modules and choosing interactive run type 1        |       |  |

| D.4                                                                       | 4 Entering the process dependent descriptors                                  |       |  |

| D.5                                                                       | 5 Entering the command file name to save the entered data $\ldots$ $\ldots$ 1 |       |  |

| D.6                                                                       | 5 Entering VDD scaling descriptors                                            |       |  |

| D.7                                                                       | Entering modules descriptors for each module in the system                    |       |  |

| D.8                                                                       | 8 Entering design choices for each module in the system                       |       |  |

| D.9                                                                       | System power and performance for the chosen module design choices $\ . \ .$   | 153   |  |

| D.10 EIDA tool used in batch mode from the command prompt. A command file |                                                                               |       |  |

|                                                                           | corresponding to the modules in the system and their respective design        |       |  |

|                                                                           | choices has to be created prior to invoking EIDA from the command             |       |  |

|                                                                           | prompt                                                                        | 154   |  |

# LIST OF TABLES

| 3.1 | Descriptors from legacy design                                           |    |  |

|-----|--------------------------------------------------------------------------|----|--|

| 3.2 | Target process technology descriptors                                    |    |  |

| 3.3 | Circuit-level design choices requiring In-situ simulations               |    |  |

| 3.4 | Descriptor vector elements from in-situ simulations                      |    |  |

| 3.5 | Algorithm ST_size_evaluate                                               |    |  |

| 3.6 | Algorithm ABB_evaluate                                                   | 65 |  |

| 4.1 | Benchmark circuit details                                                | 72 |  |

| 4.2 | Assumed descriptor and coefficient values for 180 $nm$ TSMC to 130 $nm$  |    |  |

|     | PTM technology porting                                                   | 73 |  |

| 4.3 | Module-granular circuit-level design choices                             | 74 |  |

| 4.4 | Assumed descriptor and coefficient values for 180 $nm$ to 130 $nm$ PTM & |    |  |

|     | 130 $nm$ to 90 $nm$ PTM & 90 $nm$ to 65 $nm$ PTM & 65 $nm$ to 32 $nm$    |    |  |

|     | PTM                                                                      | 77 |  |

| 4.5 | Assumed descriptor and coefficient values for 65 $nm$ to 32 $nm$ PTM     | 82 |  |

| 4.6 | Valid available additional design choices                                | 83 |  |

| 4.7 | Seed recipes for pareto-front analysis                                   | 83 |  |

| 4.8 | Summary of evolutionary algorithm based pareto analysis                  | 87 |  |

| 5.1 | Technology mode migration results                                        | 90 |  |

| 5.2 | Circuit C5315 migration results                                          | 91 |  |

| 5.3 | Circuit C6288 migration results                                          | 92 |  |

| 5.4  | Circuit C7552 migration results                                             |     |  |

|------|-----------------------------------------------------------------------------|-----|--|

| 5.5  | Circuit S38584 migration results                                            |     |  |

| 5.6  | Circuit S132007 migration results                                           |     |  |

| 5.7  | Circuit S38417 migration results                                            |     |  |

| 5.8  | Circuits S15850 & S9234 migration results                                   |     |  |

| 5.9  | EIDA and SPICE comparison                                                   | 102 |  |

| 5.10 | Modular design choices for designs #14, #13, #8 and #10 $\ldots$            | 105 |  |

| 5.11 | 1 Power and performance sensitivity of selected model parameters $\ldots$ . |     |  |

| 5.12 | Power and performance sensitivity of selected model parameters with re-     |     |  |

|      | duced de-coupling capacitance                                               | 123 |  |

# Chapter 1 Introduction

# 1.1 CMOS Technology Scaling

CMOS being the dominant technology used in VLSI systems has scaled well into deep sub-micron (DSM) sub 100 nm feature sizes. CMOS technology scaling is expected to continue the current trend and scale into sub 10 nm feature sizes in the coming decades. Current state-of-the-art production CMOS process has a minimum feature size of 45 nm and 32 nm technologies are currently being piloted for production. The semiconductor industry road map predicts that CMOS technologies with a minimum feature size of 6 nm will be developed by the year 2020 [4]. The benefits of technology scaling include reduced manufacturing cost per transistor, reduction in energy per logic function implemented on chip, and increase in the number of logic functions (i.e. transistors) that can be integrated on a single die. As feature sizes reduce, the evaluation time required for a logic function implemented in these technologies reduce due to faster transistor switching times. Reduction in evaluation time translates into an increase in the number of evaluations completed per unit time, in other words, an increase in performance. Improved performance and the reduced cost of integrating logic functions on chip are very favorable for business. The economic benefits of scaling have been very tangible and companies want this trend to continue well into the future.

Moore's Law [5] states that the number of transistors in a chip and the chip operating frequency double every eighteen months. Global semiconductor industry competitive landscape dictate that semiconductor companies abide by this law and scale their manufacturing process to stay relevant in the globalized market place. In addition to device size the operating frequency also doubles every eighteen months. As a result, designs in scaled technologies become faster. Due to the higher integration potential of the scaled technologies, designs have become bigger, more powerful and more capable in terms of functionality. For example, technology scaling has enabled microprocessor companies to design microprocessors with higher operating frequency compared to their preceding generation designs. A recent high performance microprocessor designed in a 65 nm SOI process operates at a core clock frequency of 4.7 GHz [6].

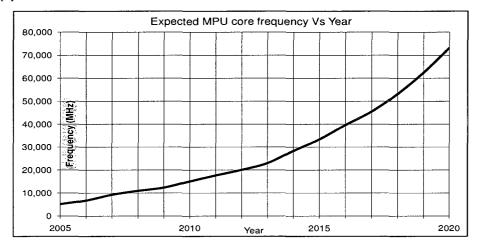

Figure 1.1: ITRS clock frequency trend up to the year 2020

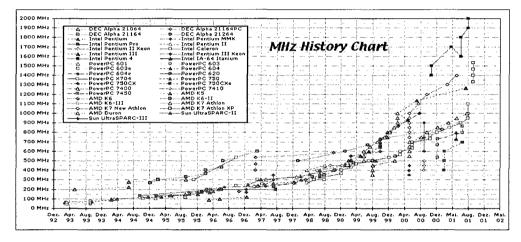

The ITRS (international technology road-map for semiconductors, predicts the core operating frequency for high performance microprocessor as shown in Fig 1.1. At present CMOS technologies with minimum feature size in the range of few tens of nanometers are becoming relatively commonplace allowing higher operating frequencies [7, 8]. As shown in Fig 1.1 the projected microprocessor core operating frequency for the next decade is upwards to 73 GHz. Aggressive scaling enables designer to design chip that meet the ever increasing demands of increased functionality by scaling designs to newer and advanced CMOS processes. In addition to increased functionality the newer technologies enable designs with higher operating frequencies. Fig 1.2 [9] shows the microprocessor core operating frequency trends in the past, i.e. from the December 1995 to May 2002.

Figure 1.2: Clock rate for high performance microprocessors from Dec '92 to May '02

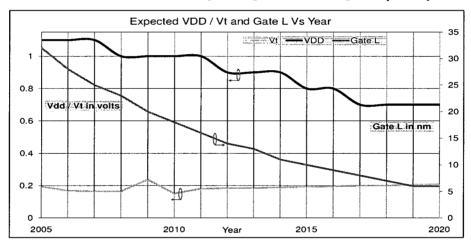

Technology scaling along with its benefits has numerous challenges. A very important challenge is the closing gap between the supply voltage  $V_{dd}$  and threshold voltage  $V_t$  as shown in Fig 1.3. This means that the transistor cannot be turned off effectively and thus lead to a dramatic increase in leakage currents. The increase in leakage is further compounded by the decreasing transistor lengths which lead to a decrease in  $V_t$ . Leakage power consumption in state-of-the-art high performance microprocessor designs can be as much as 30 to 40% of the total power consumption. Due to the higher levels of integration the total switching capacitance load (normalized to technology) increase. Higher operating frequencies leading to higher switching rates result in an increase in thermal induced instabilities and switching related signal integrity uncertainties. Another direct impact of scaling is the explosion in the number of interconnects, particularly long global interconnects as the die sizes increase. Increasing interconnect densities will lead to a reduction in signal integrity and preventive measures to improve signal integrity, which are costly are often necessary. With increasing operating frequency and distances, global signals have to travel faster and longer than they did earlier resulting in an increased need for repeaters in global interconnects. Consequently resulting in tighter delay tolerance, design tolerance and an increase in repeater power consumption [10–12].

Figure 1.3: Transistor L,  $V_{dd}$  and  $V_t$  through 2020

## 1.1.1 Technology Scaling and System Level Design

The effects of technology scaling impact the design process of a VLSI system in a number of different ways. Notably technology scaling exasperates the effect of manufacturing process variation. When the critical dimension or the minimum feature sizes (CD) reduces, the tolerance in manufacturing variation can approach the CD or be the same order of magnitude as the CD. Therefore manufacturing variations can significantly alter gate delay, interconnect delay, threshold voltage  $V_t$ , gate oxide thickness  $t_{ox}$ , gate area, leakage current variations and SRAM stability among many others, leading to increased design uncertainties. In addition to manufacturing variability lithographical limitations impact device and interconnect characteristic and composition.

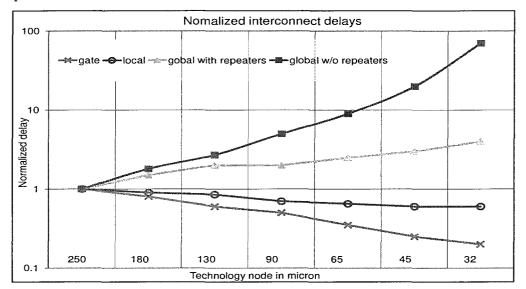

Figure 1.4: ITRS Roadmap for gate and wire delay through process nodes

Fig 1.4 shows the growth in wire delay through various process technologies. Global interconnects have become performance limiters at the system level due to exponentially increasing wire delays. Interconnect composition (width, pitch and thickness) variations causes uncertainties in interconnect delays [13]. To include interconnect uncertainties designers focus on the worst case which results in pessimistic over designing of interconnect drivers and increased power consumption. It is very important to accurately estimate interconnect delay as the critical path delay has a significant interconnect delay component which ultimately determines system performance. The same is true for gate delay as well. The variations in gate L or W,  $V_t$  and  $t_{ox}$  manifests as uncertainties in switching speed, drain or on current ( $I_{ds}$ ) as well as leakage current. From a power consumption point of view it is very important to be able to estimate the leakage currents to ensure that the design falls within the

power envelope specification [14]. SRAM stability, negative and positive bias temperature instability [15] and SER (soft error rate) [16,17] vulnerability (all of which are strongly influenced by scaling) will determine the minimum power supply voltage  $V_{dd}$  [18], the system reliability [19] and the implementation of system level architectural error protection schemes [20]. Clearly technology scaling greatly influences key design parameters which in turn impact system level design parameters and/or system architecture.

## **1.2** Semiconductor Industry Trends and Challenges

#### **1.2.1** Business Trends

The semiconductor industry has grown approximately 16% in the past decade, with 9 to 10X revenue growth to around 200 billion dollars annually. The projected growth for this industry in the next ten years is 6% annually with a projected revenue of approximately 700 billion dollars annually by 2017 [21]. Microprocessors are the most important of all semiconductor products and represents the high end of the semiconductor industry's product line. The fierce competition in this market segment compels companies to maintain an edge over their rivals to retain market share. In the past decade, quick and successive introduction of new microprocessor architectures or process technology improvements have proved to be a successful strategy to maintain market share and profitability. Current leading microprocessor design companies try to introduce new process technology or architectural advancements once every two years.

The two year cycle in the microprocessor industry is increasingly difficult to maintain, the reasons are attributed to the exponentially increasing cost of building a new manufacturing or fabrication facility (fab). The cost of a 90 nm fab was US\$2

billion whereas the cost for building a 45 nm, 300 mm wafer fab which is two generations ahead of the 90 nm fab is well over US\$5 billion. Moreover the cost incurred in developing a new 45 nm process technology was 30% higher than the 90 nm process. The cost of research and development of newer (i.e. 32 nm, 22 nm, 16 nm and so on) 450 mm CMOS technology is expected to grow exponentially with each progressive technology generation [21]. Given the high capital cost of developing newer fabs and technologies, it is important for semiconductor companies to have very short design cycles, smaller time-to-market, fewer re-spins (prototyping for testing and validation before marketing), high yield and minimal operating cost to maintain market segment share and profit margins. Design leveraging is a strategy used my most semiconductor companies to achieve better return on investment. Design leveraging is the process of porting an existing high end design to a newer technology to release the legacy design as a newer incremental product, swiftly. Design leveraging also includes reusing parts of the existing high end design to create a product with a subset of features on the original design targeted to the lower end of the market segment or a completely different market segment. Design leveraging strategy attempts to reduce the time-tomarket for keeping the company's product lines fresh and its business attractive to investors who continually seek value and good business fundamentals.

## 1.2.2 Manufacturing Technology Cost Challenges

The lithography process, especially in the sub 100 nm CMOS technology domain had increased in complexity many folds in order to maintain high patterning quality [22] [23]. Sub-wave-length lithography (were the wave length of the light source used in the manufacturing process is larger than the intended pattern size on the wafer) and decreasing feature size tend to decrease patterning quality. The wavelength of the illumination source used in lithography has changed very little over the years and reticle enhancement techniques (RET) [24] have become commonplace to improve lithographical patterning quality. Phase-shift masks, optical proximity corrections (OPC) [25] and off-axis illumination (OAI) [26] are three major resolution enhancement technologies that have enabled optical lithography extend into the nano meter era. These techniques considerably increase the complexity of lithographical masks. OAI in particular limits the pitches and sizes of the shapes the can be patterned effecting transistor designs. Among new proposed technologies to improve lithography, extreme-UV (EUV) lithography is promising however the cost of this technology has remained prohibitive till date. An other cheaper alternative is immersion lithography which is shown to be practical, however there are many mechanical problems with this technology that needs further development [27, 28].

Sub-wave-length lithography and the additional complications introduced by phase-shift masks, OPC, OAI and other sub-resolution assist features (SRAF) increase the variability in semiconductor manufacturing. Process variations (PV) in doping densities, gate oxide thickness, field oxide thickness and gate dimension alters the characteristic of transistors by introducing uncertainties in transistor on-off currents,  $V_t$ , gate leakage and junction leakage currents [29]. Smaller the feature size more pronounced are the effect of process variation motivating the need for expensive RETs. Designers (as opposed to the technology developers) have tackled the undesirable outcome of PV by employing design for manufacturing (DFM) techniques during the design process. DFM techniques usually involve additional design rules to help improve pattern quality and reduce the impact of PV. The limitation of this technique is that as CMOS technology scales, there will be an explosion in DFM rules further restricting and complicating the design process.

Given the high cost of manufacturing, challenges remain in reducing manufacturing cost. However until a suitable and relatively inexpensive solution is identified, semiconductor companies have to contend with existing technologies and rely upon efficient design methodologies to keep cost to a minimum and thus remain profitable.

### **1.2.3** Design and EDA Tool Challenges

As explained in Section 1.2.1, design leveraging and re-optimizing existing designs have become common design approaches to reduce design cost. Since leveraged or re-optimized designs have very specific goal of either boosting performance or reducing power or optimizing both; huge cost savings are possible when designs are leveraged or re-optimized. While some of the design goals may be obtained through porting a design to a newer technology, often additional tweaking of the ported design in the newer process is necessary. Lithography challenges in the newer technology generations result in physical device topology restrictions making design convergence more difficult. In addition to these restrictions, since many features do not scale well, co-optimization and design of the devices, the circuits and the layout are absolutely essential to successfully port designs to newer technologies.

With companies opting for quick and successive introduction of newer products in the market, the time available for product design (i.e. design cycle time) reduces. This implies that design teams have to increase in size (which may not be possible or desirable) or need to be more efficient and turnout high quality designs that reduce the need for expensive re-designs and debugging. A thorough design space exploration at an early stage of a design can put the design in an optimal subspace for better convergence whereby avoiding expensive redesigns later on and improves the design team's efficiency.

Conventional design flow starts with the system architectural design followed by physical design [30]. System architects base their design decisions on expert knowledge and assumptions regarding many aspect of the physical design process. In nano-meter CMOS, however, physical implementation and design convergence of a highly optimized architectural design is not guaranteed due to increasing leakage power, process variation effects, thermal density issues, signal integrity degradation and lithographical challenges [4]. The physical design process tries to optimize and often tradeoff design objectives such as performance, power consumption, reliability and yield despite the fact that the design objective are deeply intertwined with each other [31, 32]. Under stiffer time-to-market stipulation dictated by business needs, making optimal and correct design choices at each design phase becomes imperative. This is especially true at the architectural design phase where design decision have a greater impact on design convergence. Since the physical design convergence of a highly optimized architectural design cannot be guaranteed, a quick feasibility analysis of all the architectures considered will help in choosing an architectural solution that is implementable and has a higher chance of design convergence.

Existing EDA tools typically address specific design aspect such as timing or power in an accurate and detailed manner. They do not address the overall system level design trade-off, implementation feasibility analysis, and fast turn-around what-if analysis often required for assisting designers to meet design quality and timeto-market requirement [33]. Even though a collection of existing tools may be utilized to perform the above tasks, inter-operability overhead and their nature of lower level detailed analysis makes such a concoction too slow for quick feasibility analysis required for effective design space exploration. Therefore newer design tools and design aids that incorporate system level models and are fast and sufficiently accurate need to be developed. These tools can then be used during the early design phase or architectural design phase for design space exploration and tradeoff analysis and can help in choosing optimal system design for implementation. Doing this would improve design convergence and help meeting time-to-market stipulation.

## **1.3** Motivation and Objective

Business, technology and tool challenges faced by the semiconductor industry have resulted in tighter design cycle time, increased difficulty in design convergence and a need for newer design tools and aids to improve first pass design successes. A thorough design space exploration at an early stage of a design puts the design in an optimal design subspace enabling better design convergence. Existing conventional design flows lack the ability for performing early rapid design space exploration capable of reducing the need and extent of expensive last-minute re-designs.

Most modern high performance designs tend to improve and build on comparable existing designs. Sophisticated design exploration methodology and tools are especially suited for such leveraged designs since the parameters in the system level models have higher confidence level than those for ground-up designs. The work described in this dissertation is motivated by the lack of fast and effective design space exploration tools and the shortcomings of the existing approaches. The goal of the proposed method is two folds. First, to develop a high level system modeling methodology which includes low-level physical design parameters to provide more realistic constraints for design space exploration. Second, to develop a design framework for early design space exploration consisting of the high level system models and analytical models that can be used to estimate design targets such as power consumption and (maximum operating frequency) performance.

Designing large systems such as high-end multi-core microprocessors and complex system-on-chips (SOCs) are often performed by multiple design teams in parallel with each team focusing on a portion (sub-system) of the larger system. In such an environment, compartmentalized design optimizations done by individual design teams do not guarantee global design optimality. To ensue and achieve global design optimality, a holistic approach to design tradeoff and optimization is needed [2,3]. This work focuses on performance and power optimization and tradeoff analysis during the early design space exploration phase when complete bottom-up implementation data is not yet available. The proposed analytical models include prediction models for leakage power consumption, dynamic power consumption and maximum operating frequency. Utilizing legacy design data, technology scaling trend data and allowing in-situ macro-model generation and simulation, the proposed framework is positioned for more realistic estimates of the impact of circuit level design choices for a given design. The proposed evolutionary algorithm based design space exploration methodology and the modeling of a system as a collection of modules (or sub-systems or subdesign) where the modules are independently characterized allows for modeling and analyzing large designs with large design spaces without significantly disproportionate increase in system modeling efforts.

# Chapter 2

# Background Information, Existing Methodologies and Approaches

# 2.1 Overview

Design convergence in both power and performance have become increasing difficult with increasing levels of system integration, design complexity and technology scaling related uncertainties. Consequently, early design phase design validation through power performance tradeoff analysis and design space exploration have thus become an integral part of the standard design flow. This can be performed at various stages in the design process such as;

- Power performance optimization at the system level

- Structural or logic optimization at the RTL level

- Library optimization at the physical level

- Process technology (SPICE model) optimization at the foundry level

The physical design convergence of a highly optimized architectural design in nanometer CMOS is not guaranteed. The likelihood of physical design convergence Increasing ease of use & system design flexibility, decreasing solution time

Architectural optimization at the system level Structural or logic optimization at the RTL level Library cell area optimization at the physical level Semiconductor technology related optimization at the fab Increasing solution time & complexity Decreasing system design flexibility

Figure 2.1: Design flexibility, solution time and tool complexity

of the highly optimized architectural design can be increased by performing design space exploration and design optimization at the system level based on models representing low level implementation during the early design phase. The scope and opportunities for power and performance tradeoff are maximum when the optimization is performed at the highest level of design abstraction, as illustrated in Fig 2.1. Moreover, discovering a system level power consumption excursion from the intended design target when the physical implementation is complete is far too late in the design cycle for significant remedial redesign effort without delaying time to market. Design teams recognize the potential harm in encountering this situation and try to avoid it by employing many techniques and tools. The following section reviews existing methodologies and tools for design space exploration and power performance tradeoff at various levels of abstraction.

# 2.2 System Level Power Performance Optimization

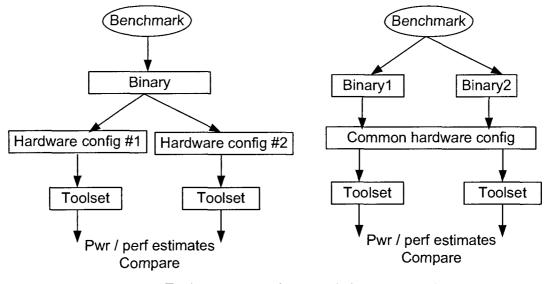

In a conventional design flow the system architectural design precedes physical implementation. System architects often use high level architectural models to explore the architectural design space to perform architectural design optimization. Fig 2.2 shows two procedures where a high level architectural model for a computational engine is utilized for architectural design optimization. These architectural models are implemented in traditional programming languages or hardware description languages. They serve to emulate the execution of standard benchmark programs on the computational engines they model. By compiling and executing well known benchmark programs, the architectural correctness and the efficiency of an architectural design can be determined very early on in the design phase.

Toolset – Any architectural simulation tool

Figure 2.2: System level optimization flows

High level architectural models have three critical and conflicting characteristics, they are model fidelity, model flexibility and model detail. Model fidelity refers to the model's ability to capture the computational engine's features such that the emulated execution of the various types workloads are close to the actual execution of the various workloads on the computational engine. Flexibility indicates the model's ability to model a wide variety of architectural designs and the relative ease of making incremental changes to the architecture and emulating the execution of benchmark programs. Model detail pertains to the level of architectural detail incorporated in the model. For example, a execution unit may be modeled as a black box or can be modeled at a lower level of abstraction as a unit consisting of sub-units or blocks such as program counter, decode logic, ALU, multiplier unit etc.

Practically however, maximizing model fidelity, model flexibility and model detail in tandem has been proven to be difficult. Most existing system level architectural models developed to study and optimize computation engine architecture, maximize two of the three critical model characteristic often at the expense of the third. The earliest notable toolset for architectural optimization is the SimpleScalar toolset [34]. SimpleScalar toolset is a fast, flexible and accurate simulator of microprocessors based on the MIPS architecture. SimpleScalar implements a parameterized modular microprocessor model based on the MIPS-4 instruction set architecture (ISA). In the following sections existing solutions for system level design optimization are discussed.

#### 2.2.1 SimpleScalar Toolset

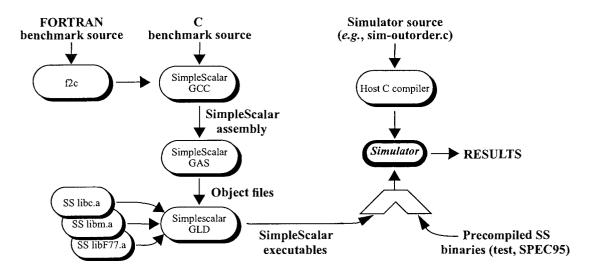

The SimpleScalar toolset provides an infrastructure for architectural design, simulation and optimization. The parameterized microprocessor model used in SimpleScalar has good fidelity and flexibility and, capable of modeling a variety of architectures ranging from a simple un-pipelined microprocessor to a complex multi cycle multiple issue out-of-order dynamic scheduling microprocessor with multiple levels of cache. The It is also easy to extend the built in microprocessor model to include additional microarchitectural features and/or to modify existing features. This allows for sufficiently detailed architectural modeling. SimpleScalar emulates the computation process in the microarchitected processor by executing the benchmark program's instructions using an instruction interpreter. Software workloads designed for popular processor architectures such as Alpha, Power PC, x86, and ARM can also be executed by using appropriate instruction interpreters for the various workloads.

Figure 2.3: An overview of SimpleScalar toolset

SimpleScalar complies binaries of the workloads (as in Fig 2.3) for the modeled architecture and emulates program execution. Thus verifying instruction execution, determining cache miss rates, estimating or summarizing execution profiles and execution time in number of processor clock cycles. The execution pipeline model used in SimpleScalar is shown is Fig 2.4. Figure 2.5 shows the SimpleScalar's internal software organization. Software workloads run on the modeled microarchitectural model using a technique called execution-driven simulation. An instruction-set emulator and an I/O emulator are utilized to interpret the workloads instructions to execute using the host platform. The instruction-set emulator interprets each compiled instruction and directs the microarchitectural models activity through callback interfaces built into the instruction interpreter.

The interpreter comprehends the nature and functioning of all the instructions in the ISA and directs the architectural model to update appropriate registers and memory state. A preprocessor uses these machine definitions to synthesize the interpreter, the dependence analyzer and the microcode generator that SimpleScalar models need to emulate program execution. The I/O emulation module provides interface to the

Figure 2.4: SimpleScalar pipeline model

| User programs      | Program Binary                               |                                  |  |

|--------------------|----------------------------------------------|----------------------------------|--|

| Prog/Sim interface | Target ISA I/O Interface                     |                                  |  |

| Functional Core    | Target ISA Emulator                          | I/O Emulator                     |  |

| Performance core   | B-Pred<br>Simulat<br>Resource<br>Cache Loder | Cor Core Stats Debug Regs Memory |  |

|                    | Host Interface                               |                                  |  |

|                    | Host platform                                |                                  |  |

Figure 2.5: SimpleScalar internal organization

external host's input and output sources. The I/O interface translates a system call in the emulated program execution into an equivalent host operating system's system call. After executing the system call the I/O interface handles the returning of the results back to the emulated program. In this manner any program written for a particular instruction set architecture (ISA) can be interpreted and executed on any host playform. This is called execution driven microarchitectural simulation.

Execution driven approach provides access to all data produced and consumed during program execution. These values are crucial to the understanding data and control flow, prediction optimizations, memory compression and dynamic power analysis. In dynamic power analysis, the simulation must monitor the data values sent to all microarchitectural components such as the arithmetic logic units and the caches to gauge switching activity which consumes power. Execution driven microarchitectural simulation also permits greater accuracy in the modeling of speculative branch prediction or load address speculation. Speculative execution causes miss-predictions, when a miss-prediction is detected later on during program execution, the pipeline is flushed and restarted with the instruction preceding the miss-prediction. Speculative instruction executions cause resource conflicts with nonspeculative instructions potentially slowing the program, this can be studied only with execution driven microarchitectural simulation. Trace-driven techniques cannot model speculative code execution because instruction traces record only correct program execution. Thus, execution driven simulation faithfully reproduces the speculative computation and correctly models its impact on program performance. Execution driven microarchitectural simulation, as in SimpleScalar, is therefore considered better than the leading alternative i.e. trace based microarchitectural simulation. The use of SimpleScalar in evaluating and optimizing different system architectures for throughput and chip area is illustrated in [35].

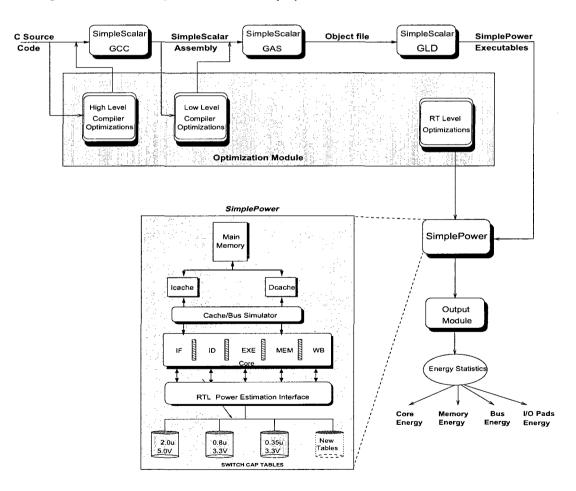

### 2.2.2 SimplePower Toolset

A major limitation of the SimpleScalar toolset is the lack of a power estimation tool in the toolset. It may be recalled that SimpleScalar does provide activity factors for various microarchitectural blocks under a variety of workloads. However just activity factors alone are not sufficient to estimate power consumption. SimplePower [36] an extension to SimpleScalar, is an input transition-sensitive execution-based cycleaccurate power estimation tool. Essentially SimplePower is a set of C-based post processing procedures to perform simulator independent process technology dependent power estimation. SimplePower assumes a five stage pipelined data path, consisting of the fetch stage (IF), the instruction decode stage (ID), the execution stage (EXE), the memory access stage (MEM), and the write-back stage (WB). Figure 2.6 shows the organization of SimplePower toolset [37].

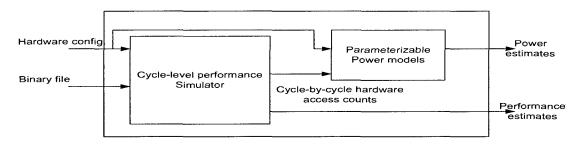

Figure 2.6: SimplePower internal organization

While executing a compiled benchmark workload, SimpleScalar, at each clock cycle, simulates the execution of all active instructions, while SimplePower monitors the activity and calls corresponding to the power estimation interfaces for all activated microarchitectural blocks. SimplePower maintains a pre-calibrated technology dependent switching capacitance table for each microarchitectural block in the design such as the adders, the ALUs, the multipliers, the shifter, the controllers, the register file, the pipeline registers and the multiplexors. The built-in bus simulator snoops and records the total number of accesses and the number of transitions on the instruction cache address bus, the instruction cache data bus, the data cache address bus, and the data cache data bus. The recorded number of accesses are combined with analytical interconnect power models to compute the effective switch capacitance of the on-chip buses. The cache simulator simulates the cache access activity and records them. SimplePower then estimates the power consumption by using a lookup table containing the switching capacitance for each input transition for every microarchitectural block activated.

### 2.2.2.1 Switching Capacitance Table Construction

SimplePower's power estimation accuracy depends on the accuracy of the switching capacitance tables. The construction of these tables is based on the structure of the microarchitectural block. All microarchitectural blocks fall into one of the following types: bit-independent microarchitectural block or bit-dependent microarchitectural block. In a bit-independent microarchitectural block, the bit slices operate independent of each other. Thus only a small bit slice switching capacitance table is needed. The total energy consumed by the microarchitectural block can be calculated by summing the energy consumed by each bit slice during transition. Bit-independent functional units include the pipeline registers, the logic unit in the ALUs, latches and buses. In a bit-dependent microarchitectural block, the bit slices are not independent of each other. In such cases energy characterization is based on input vector differences i.e. the total bit flips between two adjacent inputs; as shown in Fig 2.7 [36].

| Index        |                          | Switch          |

|--------------|--------------------------|-----------------|

| previous     | $\operatorname{current}$ | Capacitance     |

| input vector | input vector             | (pF)            |

| $0_10_n$     | $0_10_n$                 | $cap_0$         |

| $0_10_n$     | $0_11_n$                 | $cap_1$         |

| $0_10_n$     | $0_110_n$                | $cap_2$         |

| $0_10_n$     | $0_111_n$                | $cap_3$         |

|              | •••                      | •••             |

| $1_11_n$     | $1_110_n$                | $cap_{2^n-2}$   |

| $1_{11_{n}}$ | $1_111_n$                | $cap_{2^{n}-1}$ |

Figure 2.7: SimplePower switching capacitance table for bit-dependent microarchitectural blocks

For large microarchitectural blocks with a large input vector size, observing that the size of this table grows exponentially, two remedial measures were included. They are; analytical transition independent power modeling and partitioning of large microarchitectural blocks into smaller ones. Analytical modeling involves approximating the switching capacitance based on other observable parameters depending on the microarchitectural block. Partitioning of the microarchitectural blocks into smaller blocks does not require any additional changes to the toolset, only the number of microarchitectural blocks will increase.

## 2.2.3 Wattch Toolset

The Wattch toolset [38] similar to SimplePower is an extension of SimpleScalar and can be used to analyze and optimize microprocessor architectures and power dissipation. Wattch features a parameterized power model for common microarchitectural blocks found in modern superscalar microprocessors. These power models are integrated into the SimpleScalar architectural simulator toolset to form the Wattch toolset.

Figure 2.8: Wattch internal organization

Figure 2.8 shows the illustrates the internal organization of Wattch, showing the interface between the architectural simulator and the power models. Wattch's power modeling methodology classifies microarchitectural block commonly found in a microprocessor into four categories. They are;

• Array Structures: Data and instruction caches, cache tags, register files, register mapping table, branch history tables, and instruction / data load store queue.

• Fully Associative Content Addressable Memories: Instruction reorder buffer and translation look aside buffers.

• Combinational Logic and Wires: Control logic, dependency check logic and all signal buses.

• Clocking: Clock buffers, clock wires, and capacitive loads.

The power for each microarchitectural block is given by the product of the total load capacitance (C), frequency (f), square of supply voltage ( $V_{dd}$ ) and activity factor ( $\alpha$ ) i.e. ( $P_d = C \times \alpha \times f \times V_{dd}^2$ ). Power supply voltage and frequency depend on the process technology used for the design. The activity factor for all microarchitectural blocks are estimated while the cycle accurate simulator, i.e. SimpleScalar, executes the benchmark programs. The exception to obtaining the activity factor from the cycle accurate simulator is when some blocks that use dynamic logic circuits that precharge and evaluate every cycle are used in the design. For such microarchitectural blocks an activity factor of 1 (unity) is assumed. For blocks where measuring activity with the cycle accurate simulator is not possible and are not using dynamic logic circuits, a base activity factor of 0.5 (random switching activity) is assumed. When clock-gating is used in the design, higher level power models modify the activity count for microarchitectural blocks selectively (based on whether the clock to a particular block is gated or not) whereby effectively lowering overall activity factor for the corresponding blocks.

### 2.2.3.1 Calculating Switching Capacitance

Switching capacitance estimation varies for the four types of microarchitectural blocks commonly found in a microprocessor. The array structure power model is parameterized based on the number of rows (entries), columns (width of each entry), and the number of read/write ports as they affect the size and number of decoders,word lines, bit lines, length of pre-decoder wires, word lines and bit lines. Power consumption of the array consists of the following components; decoder power, word line driver power, bit line discharge and output sense amplifier powers. Word line capacitance includes the diffusion capacitance of the word line driver, the gate capacitance of the memory cell and the capacitance of the word line's metal wire. The bit line capacitance of the memory cell and the capacitance of the bit line's metal wire. The total switching capacitance of the array will be the sum of all the line capacitances and the gate capacitance of the transistors in the decode and sense amplifier.

Content addressable memory structures are analyzed very similar to the array structures. However, in the content addressable memory structure tag lines and match lines are used instead of bit lines and word lines. Switching capacitance for complex logic blocks are obtained from existing published design literature [39] [40]. Switching capacitance for buses are estimated by multiplying metal capacitance per unit length and length of the wires in the buses. The bus lengths are calculated by assuming microarchitectural block sizes based on published design literature [41]. Clock network on high performance microprocessors are a significant source of power consumption. Clock power consumption consists of long clock net switching capacitance, clock buffers and clock load switching capacitance. An example showing how the switching capacitance values were obtained from the design manual of the Alpha processor is shown in [42].

## 2.2.4 AccuPower Toolset

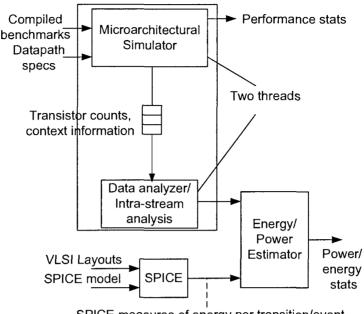

AccuPower toolset which is also based on SimpleScalar, modifies the SimpleScalar toolset and includes a power estimation tool. The AccuPower tool consists of three parts, microarchitectural simulator (modified version of the SimpleScalar toolset), physical layouts for major data path components & caches and, the power estimation module that uses coefficients obtained from SPICE simulations and transition counts obtained from the microarchitectural simulator to compute energy/power. Figure 2.9 shows the internal organization and the overall power/energy estimation methodology of the AccuPower toolset [43].

AccuPower incorporates a detailed architectural model including microarchitectural blocks such as the issue queues, the register files, the reorder buffers, the load store queues, the pipeline by-pass mechanisms, multiple levels of onchip caches, interconnections, arbitration blocks, chiplevel I/O traffic blocks and the clock distribution network. Since there is a SPICE engine involved in this toolset, design techniques such as clock gating, voltage and frequency scaling can be incorporates into the toolset allowing detailed design space exploration. For best accuracy, coefficients obtained

SPICE measures of energy per transition/event

Figure 2.9: AccuPower internal organization

from SPICE measurements of actual VLSI layouts are used. AccuPower uses parameterized models for energy dissipation for major data path components. Pipeline model improvements over SimpleScalar incorporated in Accupower include the splitting of the monolithic cache model into a two level cache model to support multiple cycle cache reads and writes, incorporating level-1 instruction and data cache, a unified level-2 cache, level-1 and level-2 cache contention, level-2 and off-chip memory contention and, a realistic multi stage multi cycle model for dispatch, register rename and operand register and read operations (these were lumped into one cycle in SimpleScalar). Therefore the microarchitectural model incorporated in Accupower is more advanced that the model used in SimpleScalar.

The focus of the AccuPower toolset is to facilitate design space exploration and gauging the impact of well understood circuit design techniques intended for saving power consumption such as clock gating, dynamic voltage and frequency scaling. AccuPower can be used to obtain realistic measurements of bit level data path activity on the interconnects and dedicated transfer links and, the read and write activities for the register files that form the data path storage components. In addition, the data analyzer modifies the switching counts based on signal bit invariance and measures the average occupancy rates for various microarchitectural blocks. The occupancy rates can be used for dynamic resource allocation studies or just resizing microarchitectural blocks. However, a major drawback of Accupower is its reliance on detailed physical layouts for all microarchitectural blocks in the design, this clearly is not possible at the early design phase when physical implementation has not been commenced and only preliminary layouts may exist.

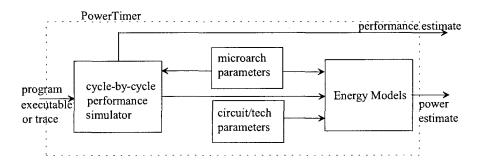

## 2.2.5 PowerTimer Toolset

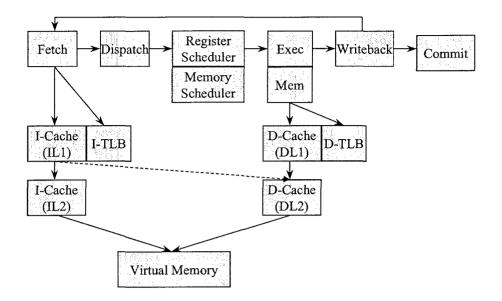

The PowerTimer [44] toolset is an early design phase microarchitectural level power performance analysis tool for modern microprocessors developed by IBM. PowerTimer consists of parameterizable energy functions that can be used in conjunction with any cycle accurate microarchitectural simulator. PowerTimer's internal organization is shown in Fig 2.10. Typically the cycle accurate microarchitectural simulator will target a particular microarchitecture, however for general architectural studies a parameterize microprocessor model, as shown in Fig 2.11, is used along with a cycle accurate simulator called Turandot.

Figure 2.10: PowerTimer internal organization

Figure 2.11: PowerTimer pipeline model

The modeled pipeline structure of the parameterized Turandot microprocessor is similar in complexity to modern microprocessors. The model has an in-order front end. The instruction fetch unit on any given cycle, accesses the level-1 instruction cache to fetch the next sequential group of instructions into the instruction buffer. The per cycle fetch window width is a parameter that the user sets. The decode/expand unit is parameterized and can decode up to five instructions per cycle to form a basic instruction dispatch group. Some complex instructions are broken down into micro operations. After the register renaming and dispatch the instructions are issued to one of the four queues; namely the integer queue, the load/store queue, the floating-point queue and the branch queue. Each instruction issue logic supports out-of-order issue to the execution units. Up to two instructions can be issued per cycle. The model also supports out-of-order execution with in-order retirement using a reorder buffer mechanism. Turandot incorporates a two level cache hierarchy i.e. a split instruction and data L1 caches and a unified L2 cache. Instruction and data translation look aside buffers are also included in the model. The main memory is considered as an infinite perfect storage with a constant parameterized access latency.

PowerTimer uses a variety of sources for developing the power models, such as detailed circuit level power analysis results, extraction tool based estimator results and analytical models derived in a bottom-up modeling methodology. Energy models can be developed based on the following methodologies;

• Microarchitectural level energy models, used in early conceptual design phase is based block level latch counts estimated by the design team. These latch counts are estimated from logic level specifications or area and latch density based projections from prior designs, suitably scaled by technology upgrade parameters. Observing that clocked latches account for 70 to 80% of logic power, a latch based energy model for non array portions of the design is adequate during conceptual phase design space exploration.

• Microarchitectural level energy models can be build on detailed macro level power (SPICE) simulation data of prior existing design. Macros that are reused in subsequent designs are characterized using detailed SPICE simulation. This method is appropriate for both the early design phase as well as the early implementation phase.

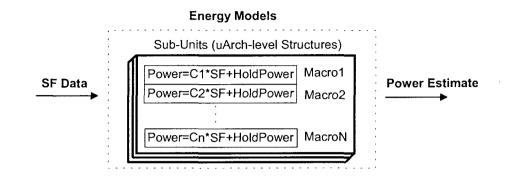

Fig 2.12 represents the hierarchial macro based power characterization methodology. Where SF (switching factor) is the average rate at which a particular microarchitectural block is called while executing benchmark workload suites. HoldPower

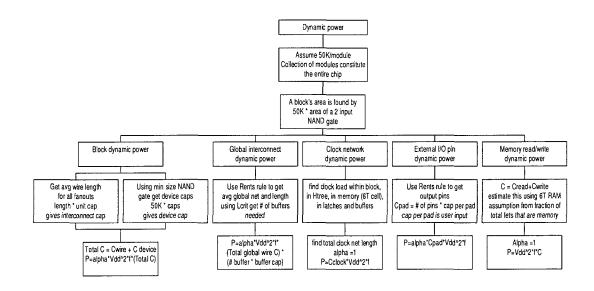

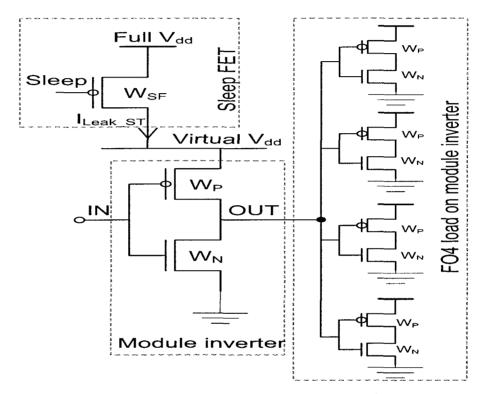

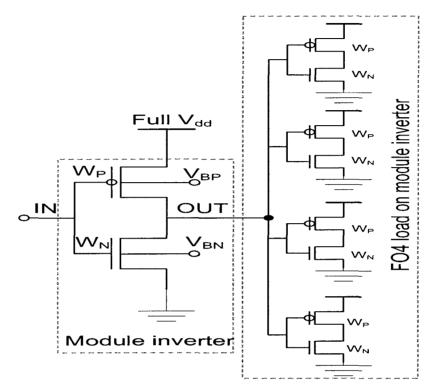

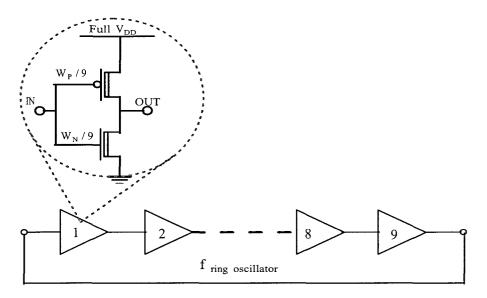

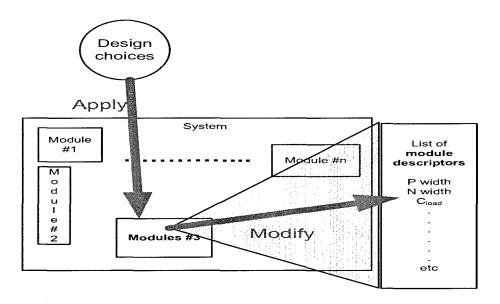

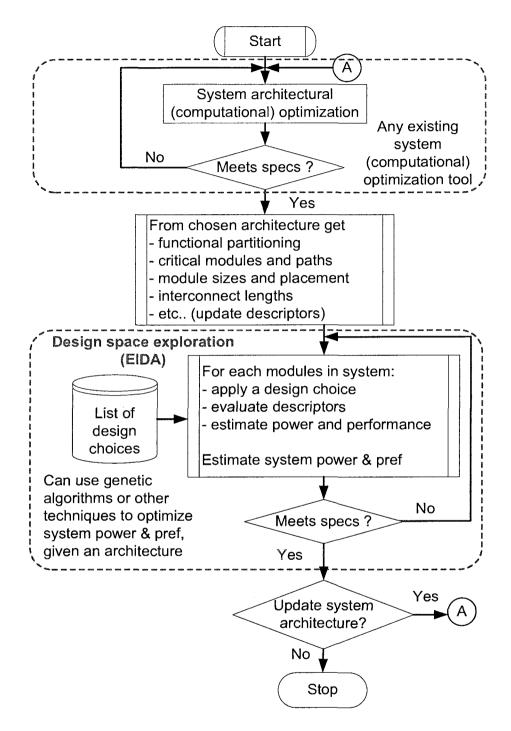

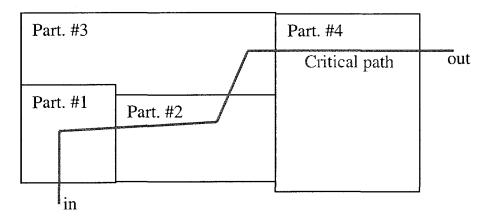

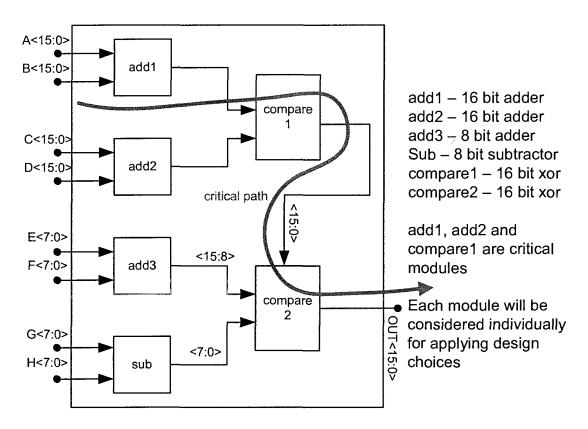

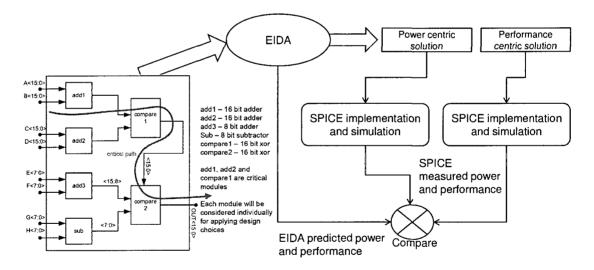

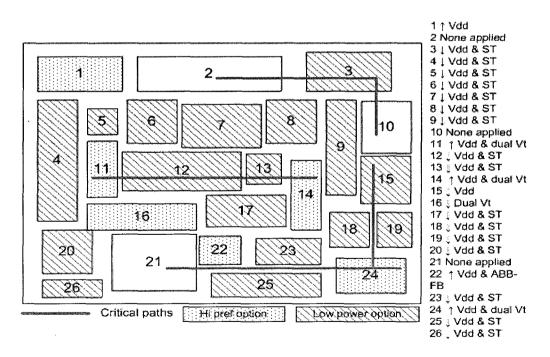

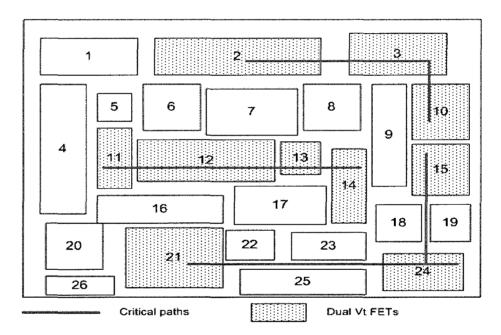

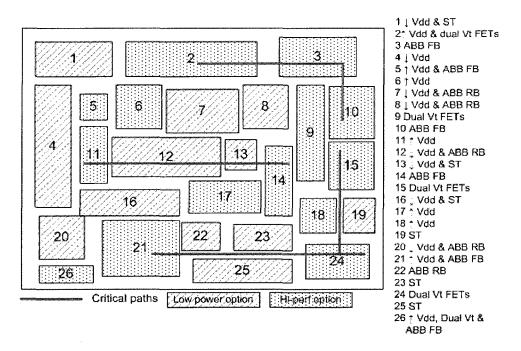

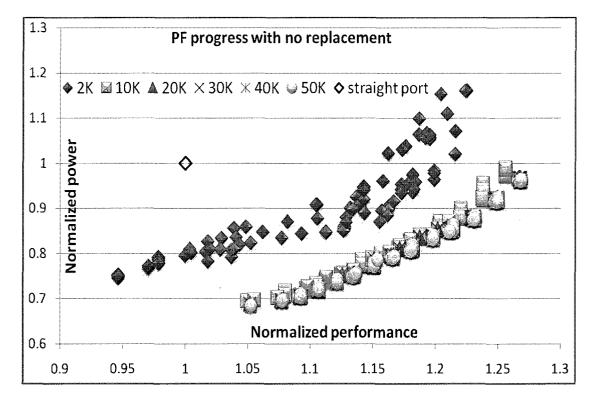

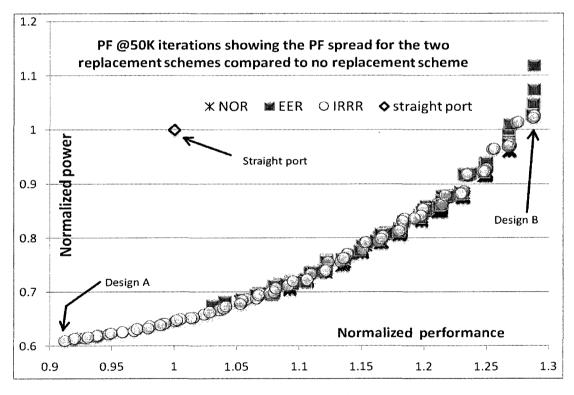

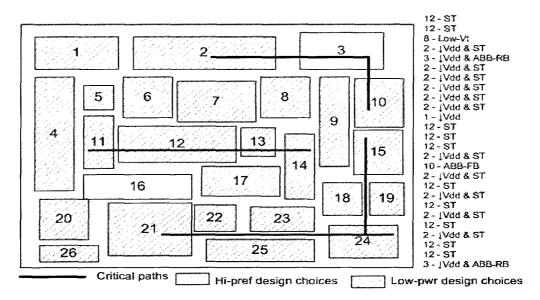

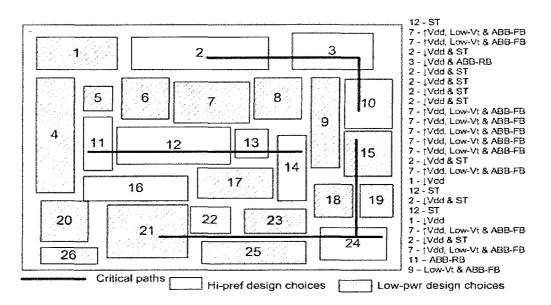

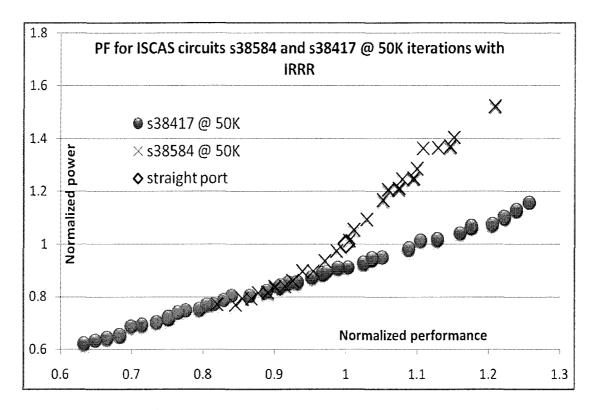

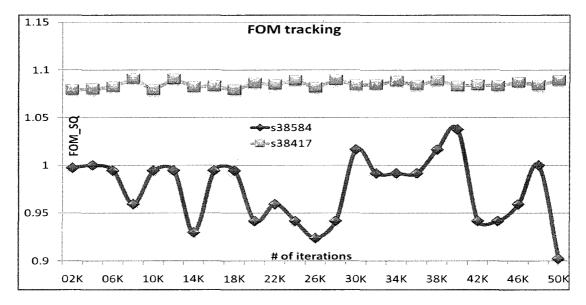

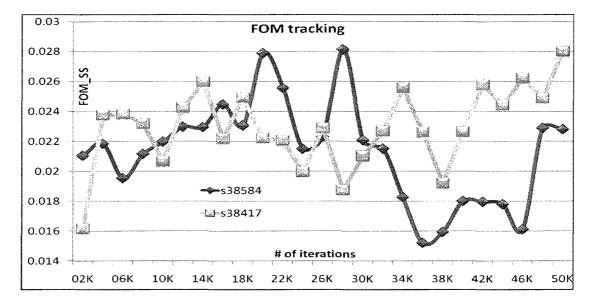

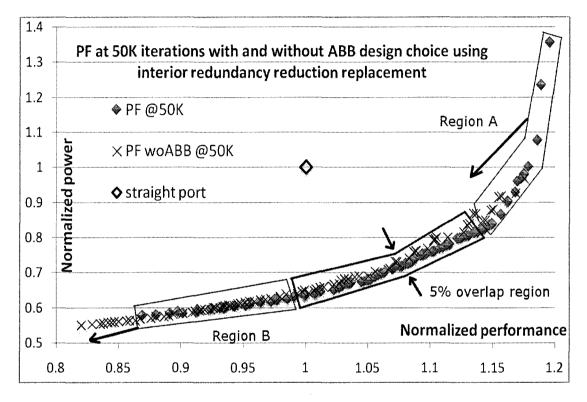

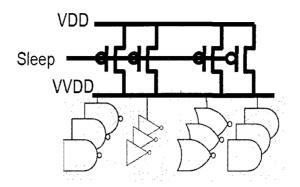

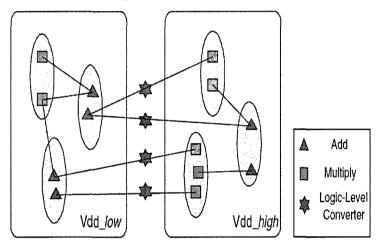

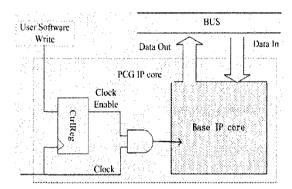

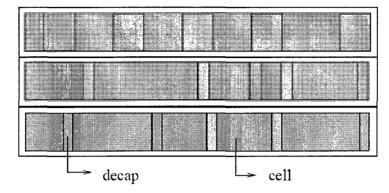

Figure 2.12: PowerTimer microarchitectural block power model